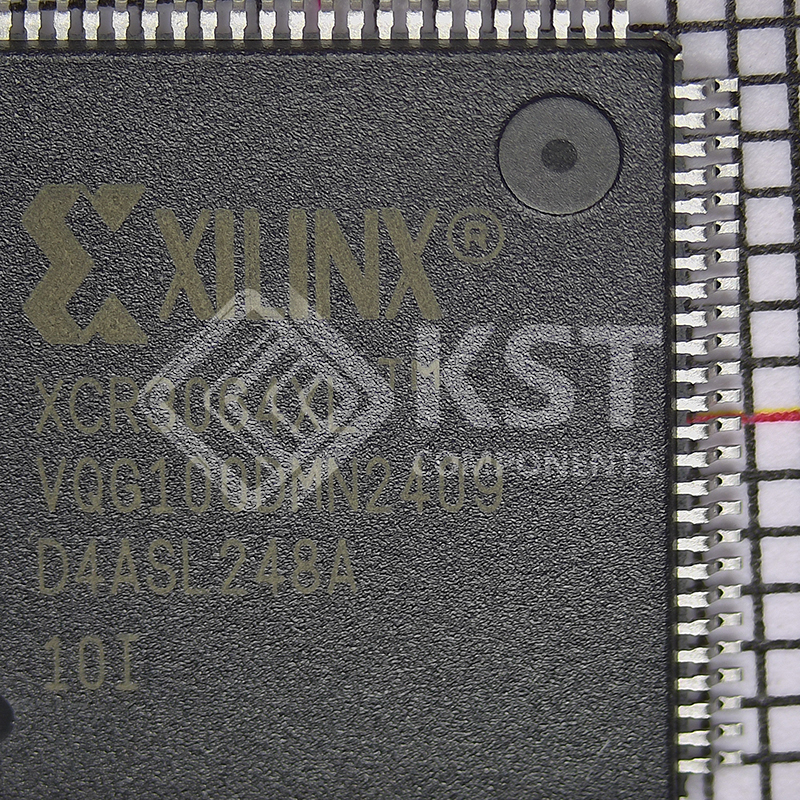

• Low power 3.3V 64 macrocell CPLD

• 5.5 ns pin-to-pin logic delays

• System frequencies up to 192 MHz

• 64 macrocells with 1,500 usable gates

• Available in small footprint packages

– 44-pin VQFP (36 user I/O pins)

– 48-ball CS BGA (40 user I/O pins)

– 56-ball CP BGA (48 user I/O pins)

– 100-pin VQFP (68 user I/O pins)

• Optimized for 3.3V systems

– Ultra-low power operation

– Typical Standby Current of 17 μA at 25°C

– 5V tolerant I/O pins with 3.3V core supply

– Advanced 0.35 micron five layer metal EEPROM

process

– Fast Zero Power CMOS design technology

– 3.3V PCI electrical specification compatible

outputs (no internal clamp diode on any input or

I/O, no minimum clock input capacitance)

• Advanced system features

– In-system programming

– Input registers

– Predictable timing model

– Up to 23 available clocks per function block

– Excellent pin retention during design changes

– Full IEEE Standard 1149.1 boundary-scan (JTAG)

– Four global clocks

– Eight product term control terms per function block

• Fast ISP programming times

• Port Enable pin for dual function of JTAG ISP pins

• 2.7V to 3.6V supply voltage at industrial temperature

range

• Programmable slew rate control per macrocell

• Security bit prevents unauthorized access

• Refer to XPLA3 family data sheet (DS012) for

architecture description