• Dual-core architecture

– Two TMS320C28x 32-bit CPUs

– 200MHz

– IEEE 754 single-precision Floating-Point Unit

(FPU)

– Trigonometric Math Unit (TMU)

– Viterbi/Complex Math Unit (VCU-II)

• Two programmable Control Law Accelerators

(CLAs)

– 200MHz

– IEEE 754 single-precision floating-point

instructions

– Executes code independently of main CPU

• On-chip memory

– 512KB (256KW) or 1MB (512KW) of flash

(ECC-protected)

– 172KB (86KW) or 204KB (102KW) of RAM

(ECC-protected or parity-protected)

– Dual-zone security supporting third-party

development

– Unique identification number

• Clock and system control

– Two internal zero-pin 10MHz oscillators

– On-chip crystal oscillator

– Windowed watchdog timer module

– Missing clock detection circuitry

• 1.2V core, 3.3V I/O design

• System peripherals

– Two External Memory Interfaces (EMIFs) with

ASRAM and SDRAM support

– Dual 6-channel Direct Memory Access (DMA)

controllers

– Up to 169 individually programmable,

multiplexed General-Purpose Input/Output

(GPIO) pins with input filtering

– Expanded Peripheral Interrupt controller (ePIE)

– Multiple Low-Power Mode (LPM) support with

external wakeup

• Communications peripherals

– USB 2.0 (MAC + PHY)

– Support for 12-pin 3.3V-compatible Universal

Parallel Port (uPP) interface

– Two Controller Area Network (CAN) modules

(pin-bootable)

– Three high-speed (up to 50MHz) SPI ports (pinbootable)

– Two Multichannel Buffered Serial Ports

(McBSPs)

– Four Serial Communications Interfaces (SCI/

UART) (pin-bootable)

– Two I2C interfaces (pin-bootable)

• Analog subsystem

– Up to four Analog-to-Digital Converters (ADCs)

• 16-bit mode

– 1.1MSPS each (up to 4.4MSPS system

throughput)

– Differential inputs

– Up to 12 external channels

• 12-bit mode

– 3.5MSPS each (up to 14MSPS system

throughput)

– Single-ended inputs

– Up to 24 external channels

• Single Sample-and-Hold (S/H) on each ADC

• Hardware-integrated post-processing of

ADC conversions

– Saturating offset calibration

– Error from setpoint calculation

– High, low, and zero-crossing compare,

with interrupt capability

– Trigger-to-sample delay capture

– Eight windowed comparators with 12-bit Digitalto-Analog Converter (DAC) references

– Three 12-bit buffered DAC outputs

• Enhanced control peripherals

– 24 Pulse Width Modulator (PWM) channels with

enhanced features

– 16 High-Resolution Pulse Width Modulator

(HRPWM) channels

• High resolution on both A and B channels of

8 PWM modules

• Dead-band support (on both standard and

high resolution)

– Six Enhanced Capture (eCAP) modules

– Three Enhanced Quadrature Encoder Pulse

(eQEP) modules

– Eight Sigma-Delta Filter Module (SDFM) input

channels, 2 parallel filters per channel

• Standard SDFM data filtering

• Comparator filter for fast action for out of

range

• Configurable Logic Block (CLB)

– Augments existing peripheral capability

– Supports position manager solutions

• Functional Safety-Compliant

– Developed for functional safety applications

– Documentation available to aid ISO 26262

system design up to ASIL D; IEC 61508 up to

SIL 3; IEC 60730 up to Class C; and UL 1998

up to Class 2

– Hardware integrity up to ASIL B, SIL 2

• Safety-related certification

– ISO 26262 certified up to ASIL B and IEC

61508 certified up to SIL 2 by TUV SUD

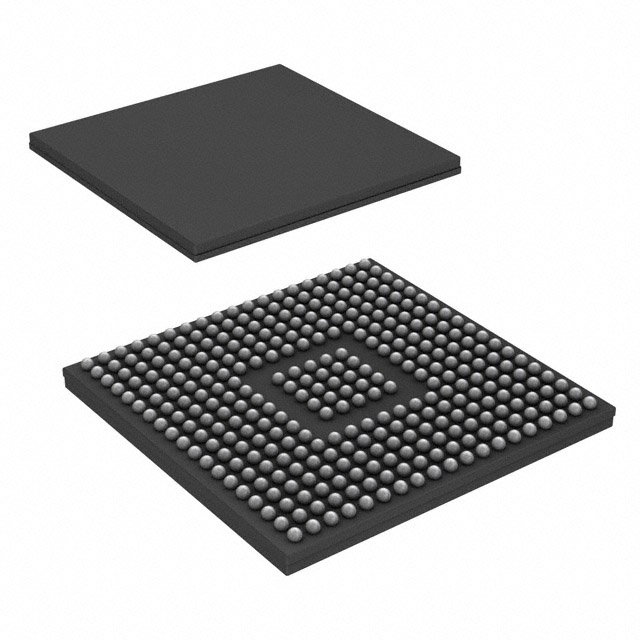

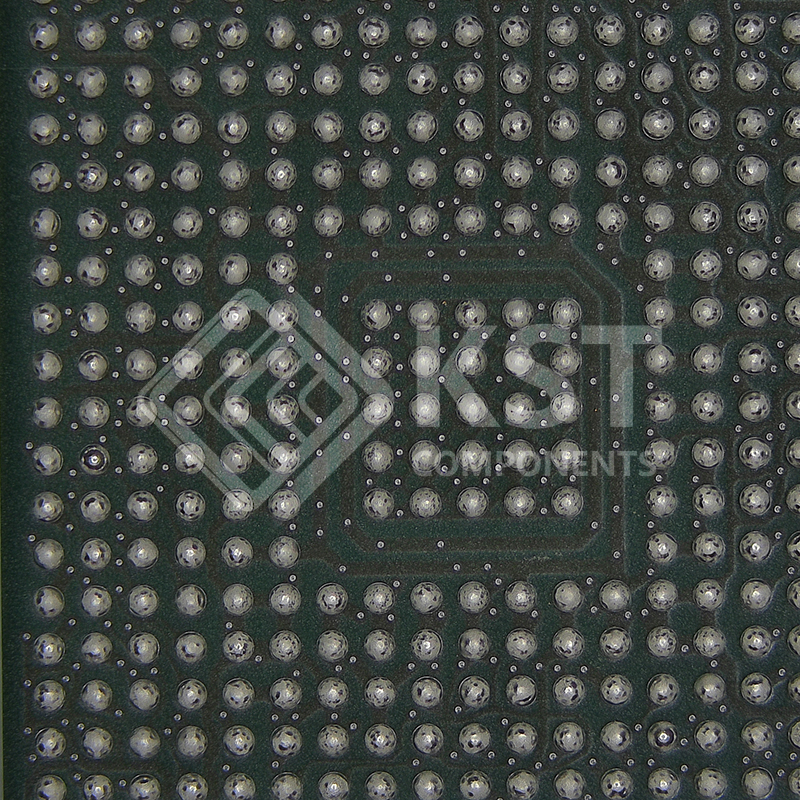

• Package options:

– Lead-free, green packaging

– 337-ball New Fine Pitch Ball Grid Array

(nFBGA) [ZWT suffix]

– 176-pin PowerPAD™ Thermally Enhanced LowProfile Quad Flatpack (HLQFP) [PTP suffix]

– 100-pin PowerPAD Thermally Enhanced Thin

Quad Flatpack (HTQFP) [PZP suffix]

• Hardware Built-in Self Test (HWBIST)

• Temperature options:

– T: –40°C to 105°C junction

– S: –40°C to 125°C junction

– Q: –40°C to 125°C free-air

(AEC Q100 qualification for automotive

applications)