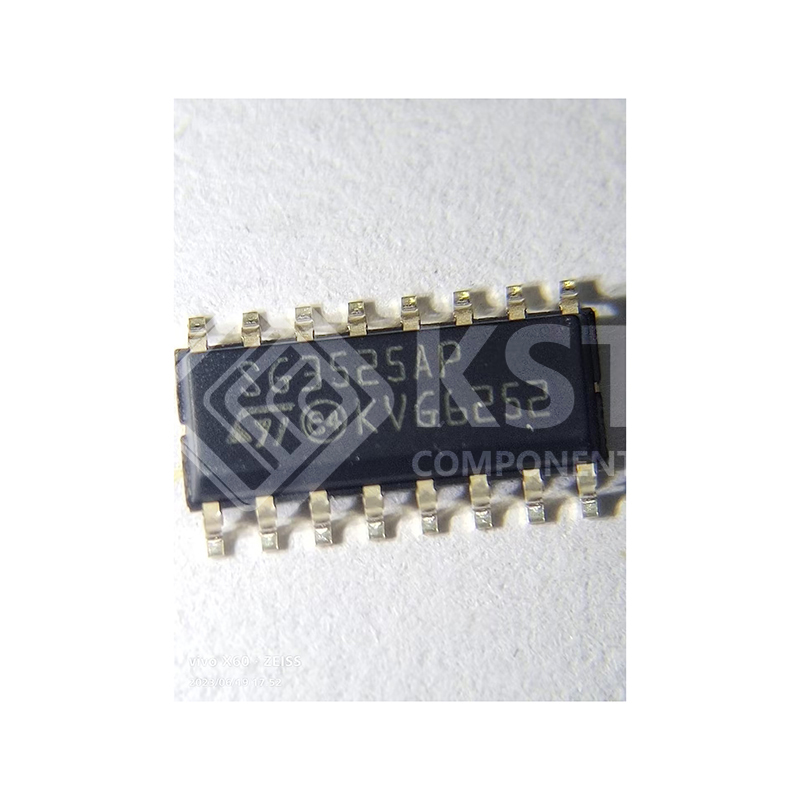

. 8 TO 35 V OPERATION

. 5.1 V REFERENCE TRIMMED TO ± 1 %

. 100 Hz TO 500 KHz OSCILLATOR RANGE

. SEPARATE OSCILLATOR SYNC TERMINAL

. ADJUSTABLE DEADTIME CONTROL

.INTERNAL SOFT-START

. PULSE-BY-PULSE SHUTDOWN

.INPUT UNDERVOLTAGE LOCKOUT WITH

HYSTERESIS

. LATCHING PWM TO PREVENT MULTIPLE

PULSES

. DUAL SOURCE/SINK OUTPUT DRIVERS