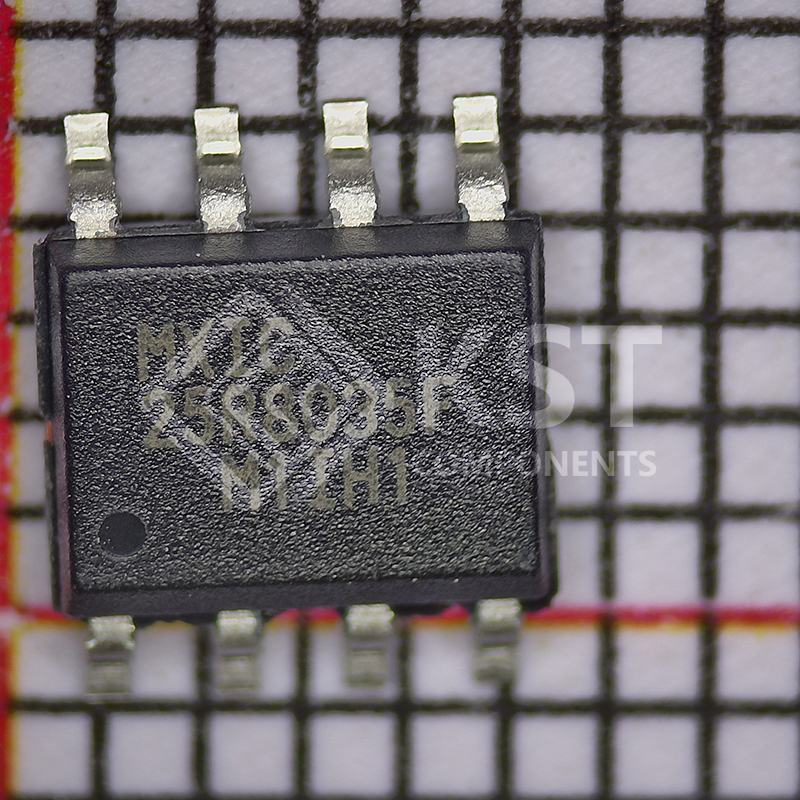

• Supports Serial Peripheral Interface — Mode 0 and Mode 3

• 8,388,608 x 1 bit structure or 4,194,304 x 2 bits (two I/O mode) structure or 2,097,152 x 4 bits (four I/O mode)

structure

• Equal Sectors with 4K byte each, or Equal Blocks with 32K/64K byte each

– Any Block can be erased individually

• Single Power Supply Operation

– Operation Voltage: 1.65V-3.6V for Read, Erase and Program Operations

• Latch-up protected to 100mA from -1V to Vcc +1V