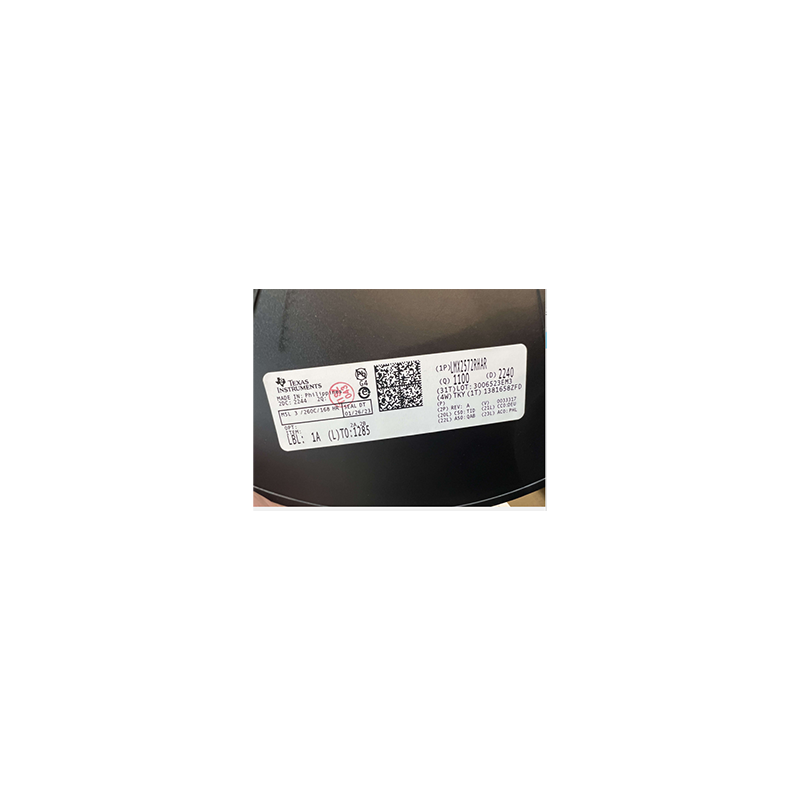

1• Output frequency: 12.5 MHz to 6.4 GHz

• Low power consumption: 75 mA at 3.3-V supply

• –106-dBc/Hz Phase noise at 100-kHz offset with

6.4-GHz carrier

• PLL figure of merit: –232 dBc/Hz

• PLL normalized 1/f noise: –123.5 dBc/Hz

• 32-Bit Fractional-N divider

• Remove integer boundary spurs with

programmable input multiplier

• Synchronization of output phase across multiple

devices

• Support for JESD204B SYSREF with

programmable delay

• Support for ramp and chirp functions

• Support for FSK direct digital modulation

• Two programmable output power level differential

outputs

• Fast VCO calibration speed: < 20 µs

• Single 3-V to 3.5-V power supply