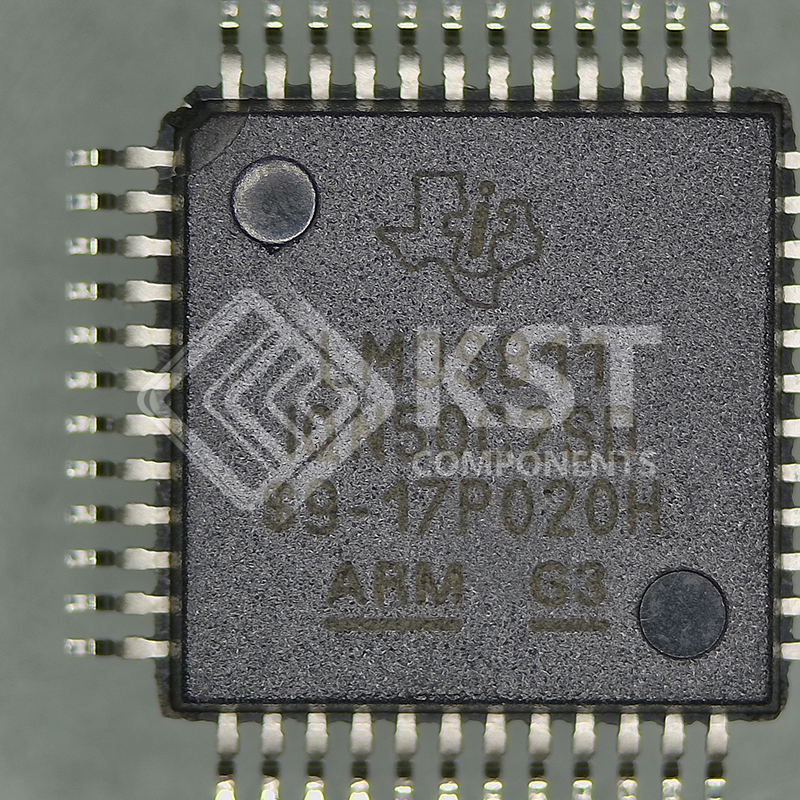

The LM3S811 microcontroller includes the following product features:

■ 32-Bit RISC Performance

– 32-bit ARM® Cortex™-M3 v7M architecture optimized for small-footprint embedded

applications

– System timer (SysTick), providing a simple, 24-bit clear-on-write, decrementing, wrap-on-zero

counter with a flexible control mechanism

– Thumb®-compatible Thumb-2-only instruction set processor core for high code density

– 50-MHz operation

– Hardware-division and single-cycle-multiplication

– Integrated Nested Vectored Interrupt Controller (NVIC) providing deterministic interrupt

handling

– 26 interrupts with eight priority levels

– Memory protection unit (MPU), providing a privileged mode for protected operating system

functionality

– Unaligned data access, enabling data to be efficiently packed into memory

– Atomic bit manipulation (bit-banding), delivering maximum memory utilization and streamlined

peripheral control

■ ARM® Cortex™-M3 Processor Core