Advanced Switch Features

• IEEE 802.1q VLAN Support for up to 128 VLAN

Groups (Full-Range 4096 of VLAN IDs)

• Static MAC Table Supports up to 32 Entries

• VLAN ID Tag/Untag Options, Per Port Basis

• IEEE 802.1p/q Tag Insertion or Removal on a Per

Port Basis Based on Ingress Port (Egress)

• Programmable Rate Limiting at the Ingress and

Egress on a Per Port Basis

• Jitter-Free Per Packet Based Rate-Limiting Support

• Broadcast Storm Protection with Percentage Control (Global and Per Port Basis)

• IEEE 802.1d Rapid Spanning Tree Protocol RSTP

Support

• Tail Tag Mode (1 Byte Added Before FCS) Support at Port 5 to Inform the Processor Which

Ingress Port Receives the Packet

• 1.4 Gbps High-Performance Memory Bandwidth

and Shared Memory Based Switch Fabric with

Fully Non-Blocking Configuration

• MII with MAC 5 on Port 5, SW5-MII for MAC 5 MII

Interface

• Enable/Disable Option for Huge Frame Size (up

to 2000 Bytes Per Frame)

• IGMP v1/v2 Snooping (IPv4) Support for Multicast

Packet Filtering

• IPv4/IPv6 QoS Support

• Support Unknown Unicast/Multicast Address and

Unknown VID Packet Filtering

• Self-Address Filtering

Comprehensive Configuration Register Access

• Serial Management Interface (MDC/MDIO) to All

PHYs Registers and SMI Interface (MDC/MDIO)

to All Registers

• High-Speed SPI (up to 25 MHz) and I2C Master

Interface to all Internal Registers

• I/O Pins Strapping and EEPROM to Program

Selective Registers in Unmanaged Switch Mode

• Control Registers Configurable on the Fly (PortPriority, 802.1p/d/q, AN…)

QoS/CoS Packet Prioritization Support

• Per Port, 802.1p and DiffServ-Based

• 1/2/4-Queue QoS Prioritization Selection

• Programmable Weighted Fair Queuing for Ratio

Control

• Re-Mapping of 802.1p Priority Field Per Port

Basis

Integrated 5-Port 10/100 Ethernet Switch

• New Generation Switch with Five MACs and Five

PHYs that are Fully Compliant with the IEEE

802.3u Standard

• Non-Blocking Switch Fabric Ensures Fast Packet

Delivery by Utilizing a 1K MAC Address Lookup

Table and a Store-and-Forward Architecture

• On-Chip 64Kbyte Memory for Frame Buffering

(Not Shared with 1K Unicast Address Table)

• Full-Duplex IEEE 802.3x Flow Control (PAUSE)

with Force Mode Option

• Half-Duplex Back Pressure Flow Control

• HP Auto MDI/MDI-X and IEEE Auto Crossover

Support

• Port 5 MAC5 SW5-MII Interface Supports PHY

Mode and MAC Mode

• 7-Wire Serial Network Interface (SNI) Support for

Legacy MAC

• Per Port LED Indicators for Link, Activity, and 10/

100 Speed

• Register Port Status Support for Link, Activity,

Full-/Half-Duplex and 10/100 Speed

• LinkMD® Cable Diagnostic Capabilities for Determining Cable Opens, Shorts, and Length

• On-Chip Terminations and Internal Biasing Technology for Cost Down and Lowest Power Consumption

Switch Monitoring Features

• Port Mirroring/Monitoring/Sniffing: Ingress and/or

Egress Traffic to Any Port or MII

• MIB Counters for Fully Compliant Statistics Gathering; 34 MIB Counters Per Port

• Loopback Support for MAC, PHY, and Remote

Diagnostic of Failure

• Interrupt for the Link Change on Any Ports

Low-Power Dissipation

• Full-Chip Hardware Power-Down

• Full-Chip Software Power-Down and Per Port

Software Power-Down

• Energy-Detect Mode Support <100 mW Full-Chip

Power Consumption When All Ports Have No

Activity

• Very-Low Full-Chip Power Consumption (<0.5W)

in Standalone 5-Port, without Extra Power Consumption on Transformers

• Dynamic Clock Tree Shutdown Feature

• Voltages: Single 3.3V Supply with 3.3V VDDIO and

Internal 1.2V LDO Controller Enabled, or External

1.2V LDO Solution

– Analog VDDAT 3.3V Only

– VDDIO Support 3.3V, 2.5V, and 1.8V

– Low 1.2V Core Power

• Industrial Temperature Range: –40°C to +85°C

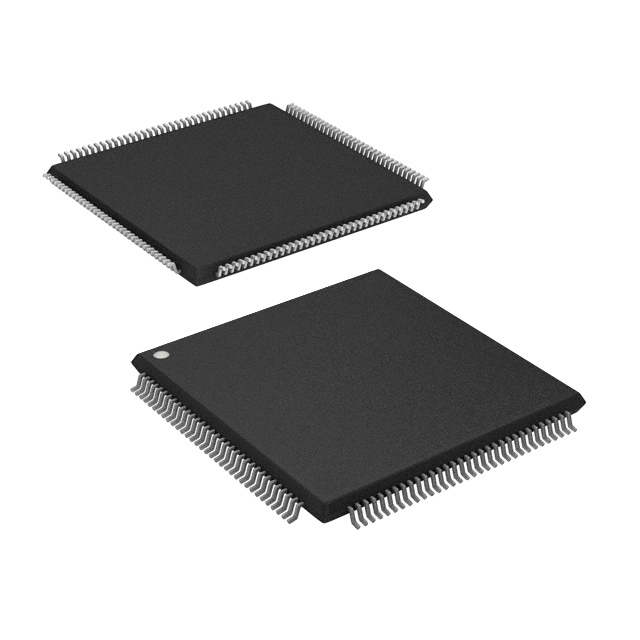

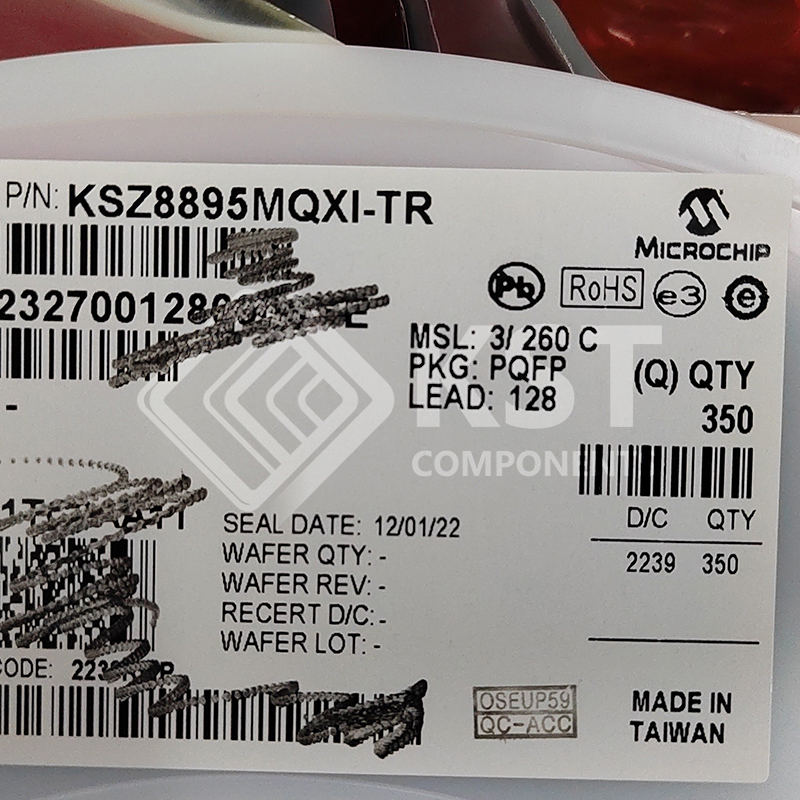

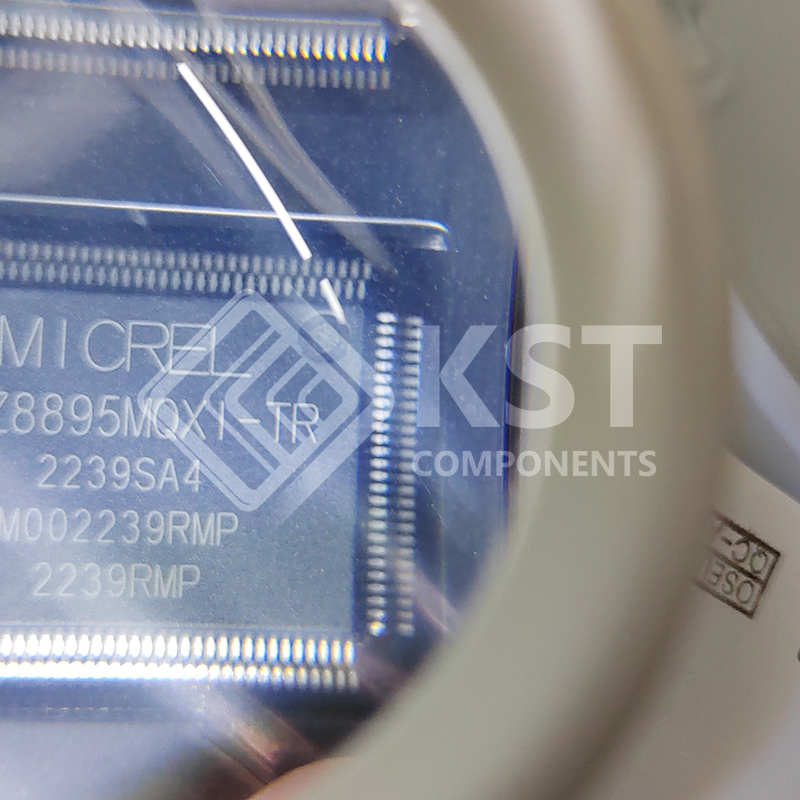

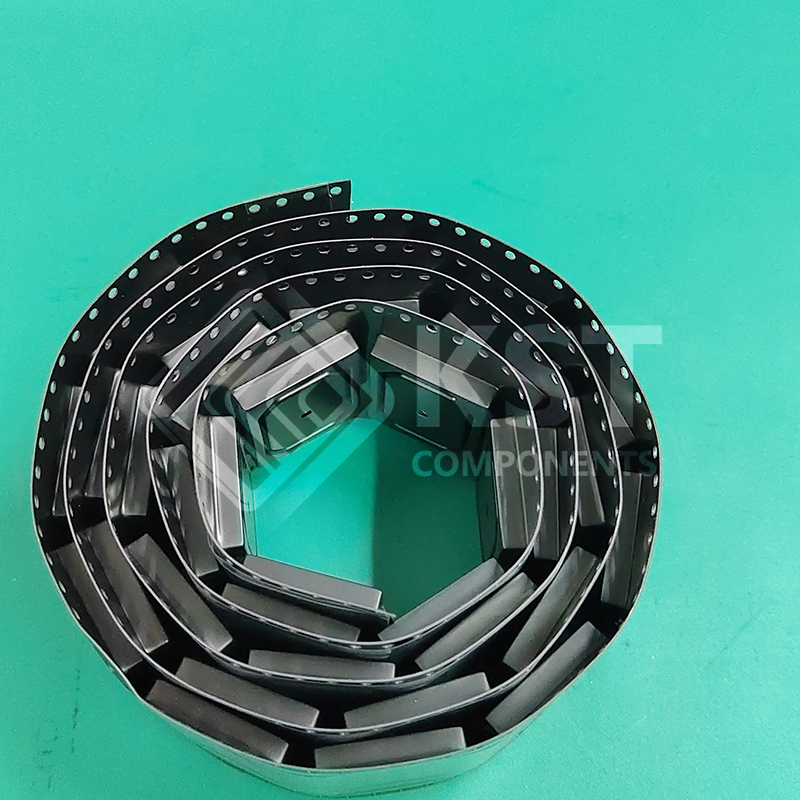

• Available in 128-pin LQFP, Lead-Free Package