■ True dual port memory enables simultaneous access the

shared array from each port

■ Synchronous pipelined operation with single data rate (SDR)

operation on each port

❐ SDR interface at 200 MHz

❐ Up to 28.8 Gbps bandwidth (200 MHz × 72-bit × 2 ports)

■ Selectable pipelined or flow-through mode

■ 1.5 V or 1.8 V core power supply

■ Commercial and Industrial temperature

■ IEEE 1149.1 JTAG boundary scan

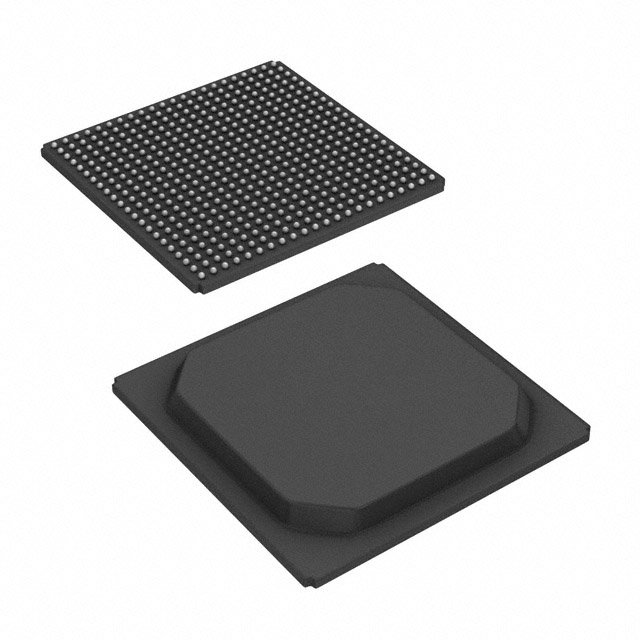

■ Available in 484-ball PBGA (× 72) and 256-ball FBGA (× 36

and × 18) packages

■ FullFlex72 family

❐ 36-Mbit: 512K × 72 (CYD36S72V18)

❐ 18-Mbit: 256K × 72 (CYD18S72V18)

❐ 9-Mbit: 128K × 72 (CYD09S72V18)

■ FullFlex36 family

❐ 36-Mbit: 1M × 36 (CYD36S36V18)

❐ 18-Mbit: 512K × 36 (CYD18S36V18)

❐ 9-Mbit: 256K × 36 (CYD09S36V18)

❐ 2-Mbit: 64K × 36 (CYD02S36V18)

■ FullFlex18 family

❐ 36-Mbit: 2M × 18 (CYD36S18V18)

❐ 18-Mbit: 1M × 18 (CYD18S18V18)

❐ 9-Mbit: 512K × 18 (CYD09S18V18)

■ Built-in deterministic access control to manage address

collisions

❐ Deterministic flag output upon collision detection

❐ Collision detection on back-to-back clock cycles

❐ First busy address readback

■ Advanced features for improved high-speed data transfer and

flexibility

❐ Variable impedance matching (VIM)

❐ Echo clocks

❐ Selectable LVTTL (3.3 V), Extended HSTL[1] (1.4 V to 1.9 V),

1.8 V LVCMOS, or 2.5 V LVCMOS I/O on each port

❐ Burst counters for sequential memory access

❐ Mailbox with interrupt flags for message passing

❐ Dual chip enables for easy depth expansion