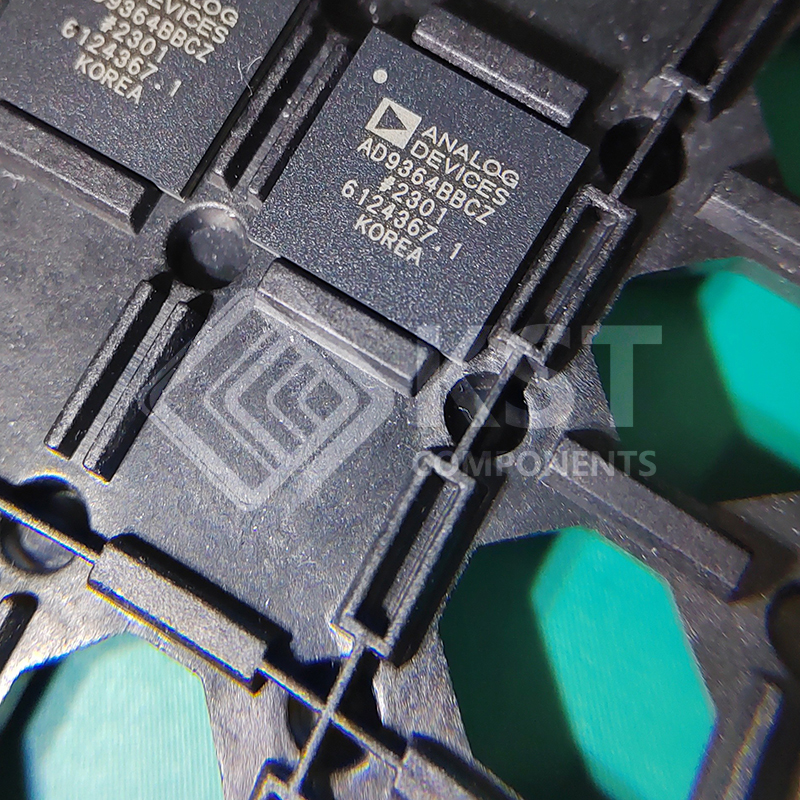

RF 1 × 1 transceiver with integrated 12-bit DACs and ADCs

Band: 70 MHz to 6.0 GHz

Supports time division duplex (TDD) and frequency division

duplex (FDD) operation

Tunable channel bandwidth (BW): <200 kHz to 56 MHz

3-band receiver: 3 differential or 6 single-ended inputs

Superior receiver sensitivity with a noise figure of <2.5 dB

Rx gain control

Real-time monitor and control signals for manual gain

Independent automatic gain control

2-band differential output transmitter

Highly linear broadband transmitter

Tx EVM: ≤−40 dB

Tx noise: ≤−157 dBm/Hz noise floor

Tx monitor: ≥66 dB dynamic range with 1 dB accuracy

Integrated fractional-N synthesizers

2.4 Hz maximum local oscillator (LO) step size

Multichip synchronization

CMOS/LVDS digital interface