• Supports SDH/SONET and Synchronous Ethernet clocks including

all FEC rate conversions

• 0.35ps RMS Typical Jitter (including spurs): 12kHz to 20MHz

• Operating Modes: Synthesizer, Jitter Attenuator

• Operates from a 10MHz to 50MHz fundamental-mode crystal or a

10MHz to 125MHz external oscillator

• Initial holdover accuracy of +50ppb.

• Accepts up to 2 LVPECL, LVDS, LVHSTL or LVCMOS input clocks

• Accepts frequencies ranging from 8kHz to 875MHz

• Auto and manual clock selection with hitless switching

• Clock input monitoring including support for gapped clocks

• Phase-slope limiting and fully hitless switching options to control

output clock phase transients

• Generates four LVPECL / LVDS / HCSL or eight LVCMOS output

clocks

• Output frequencies ranging from 8kHz up to 1.0GHz

(differential)

• Output frequencies ranging from 8kHz to 250MHz (LVCMOS)

• One integer divider ranging from ÷4 to ÷786,420

• Three fractional output dividers (see Output Dividers)

• Programmable loop bandwidth settings from 0.2Hz to 6.4kHz

• Optional fast-lock function

• Four General Purpose I/O pins with optional support for status &

control:

• Two Output Enable control inputs provide control over the four

clocks

• Manual clock selection control input

• Lock, Holdover and Loss-of-Signal alarm outputs

• Open-drain Interrupt pin

• Register programmable through I2C or via external I2C EEPROM

• Full 2.5V or 3.3V supply modes, 1.8V support for LVCMOS outputs,

GPIO and control pins

• -40°C to 85°C ambient operating temperature

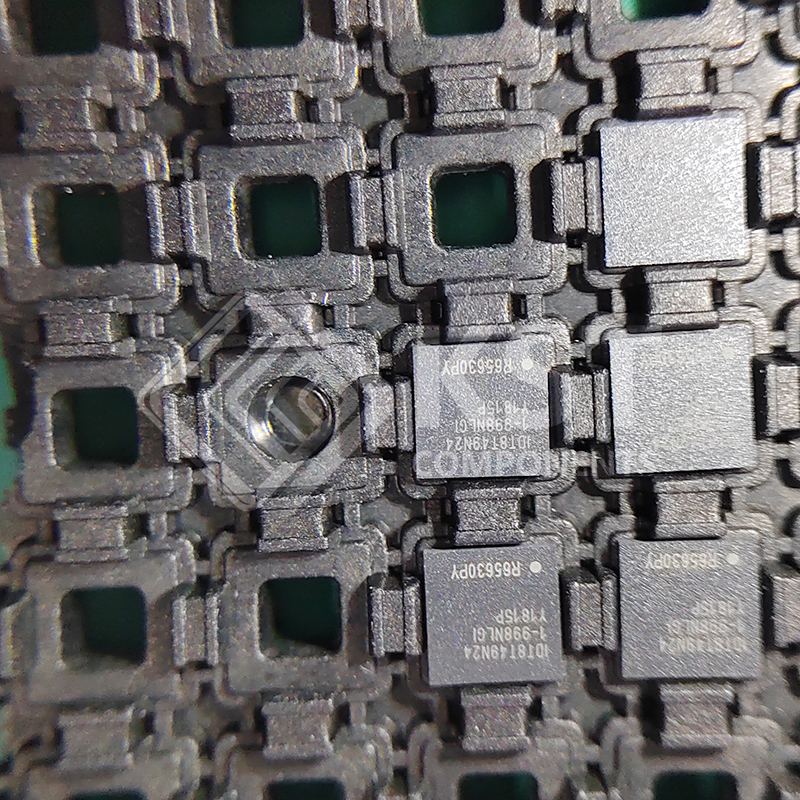

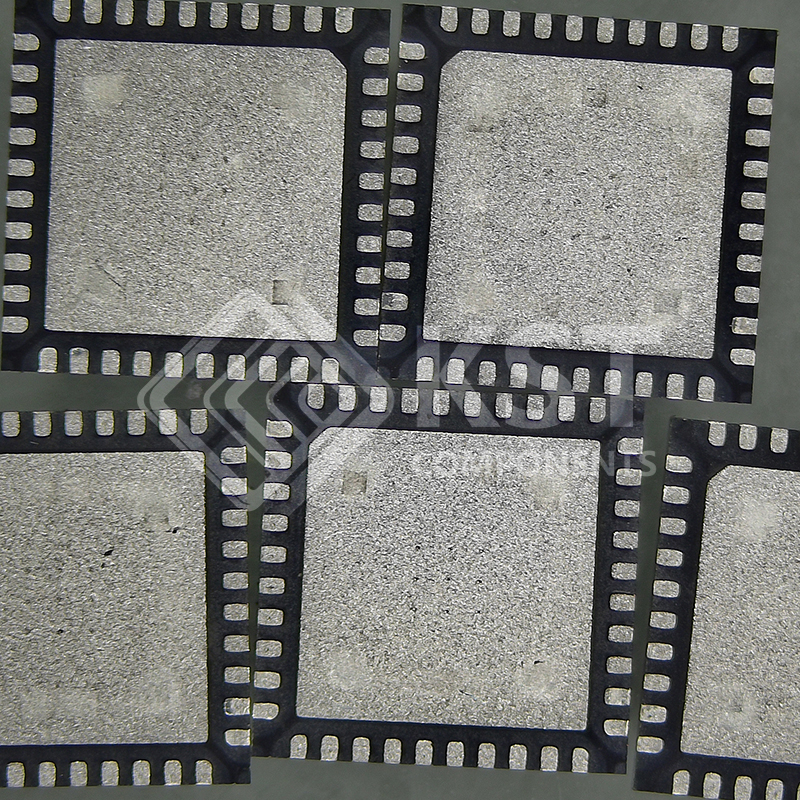

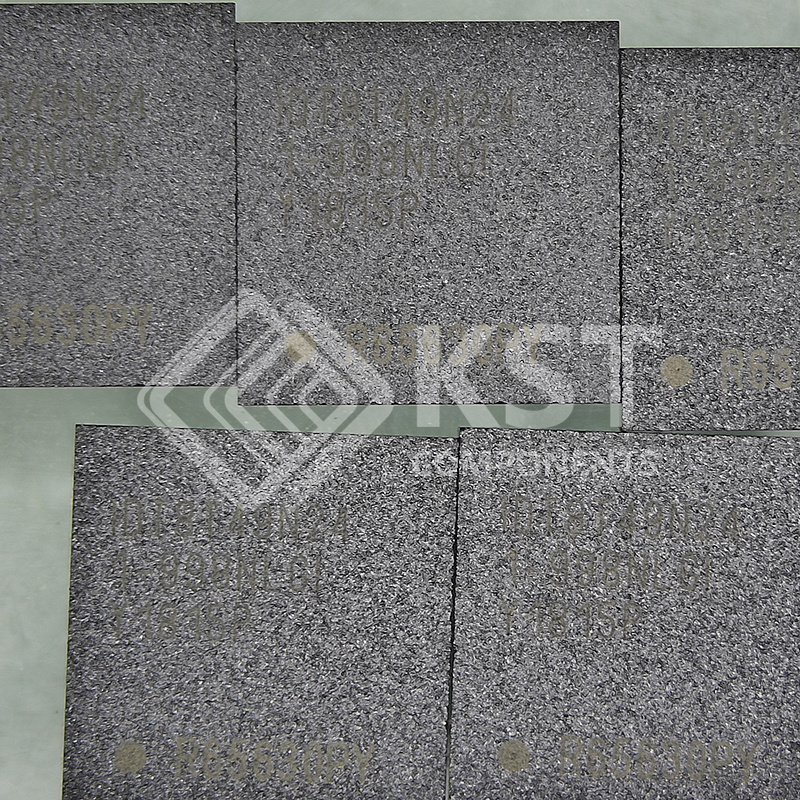

• Package: 40-VFQFPN, lead-free (RoHS 6)