■ The industry’s first embedded programmable logic device (PLD)

family, providing System-on-a-Programmable-Chip (SOPC)

integration

– Embedded array for implementing megafunctions, such as

efficient memory and specialized logic functions

– Logic array for general logic functions

■ High density

– 10,000 to 250,000 typical gates (see Tables 1 and 2)

– Up to 40,960 RAM bits; 2,048 bits per embedded array block

(EAB), all of which can be used without reducing logic capacity

■ System-level features

– MultiVoltTM I/O interface support

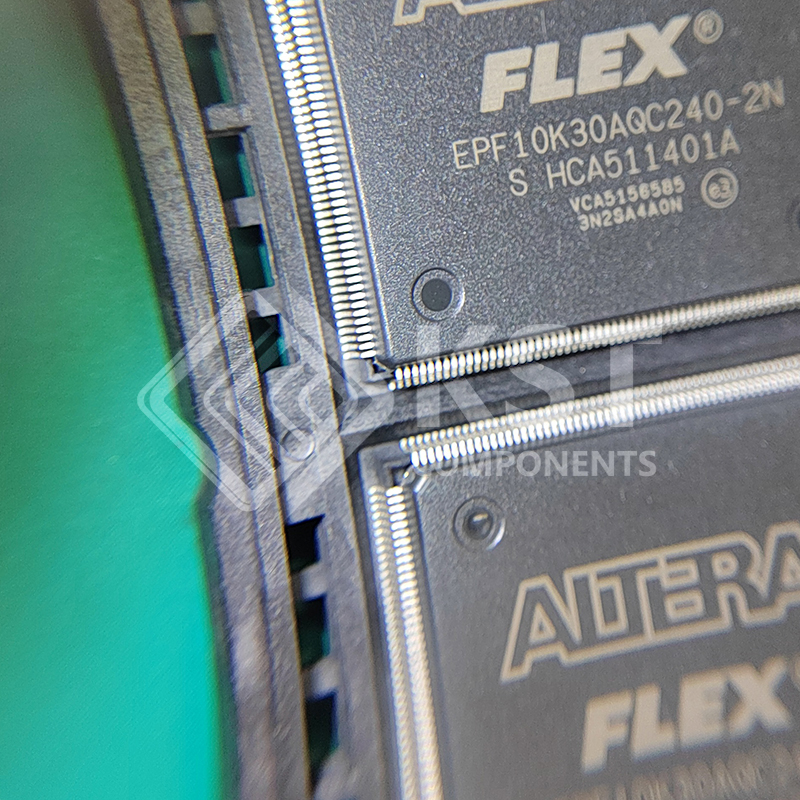

– 5.0-V tolerant input pins in FLEX® 10KA devices

– Low power consumption (typical specification less than 0.5 mA

in standby mode for most devices)

– FLEX 10K and FLEX 10KA devices support peripheral

component interconnect Special Interest Group (PCI SIG) PCI

Local Bus Specification, Revision 2.2

– FLEX 10KA devices include pull-up clamping diode, selectable

on a pin-by-pin basis for 3.3-V PCI compliance

– Select FLEX 10KA devices support 5.0-V PCI buses with eight or

fewer loads

– Built-in Joint Test Action Group (JTAG) boundary-scan test

(BST) circuitry compliant with IEEE Std. 1149.1-1990, available

without consuming any device logic