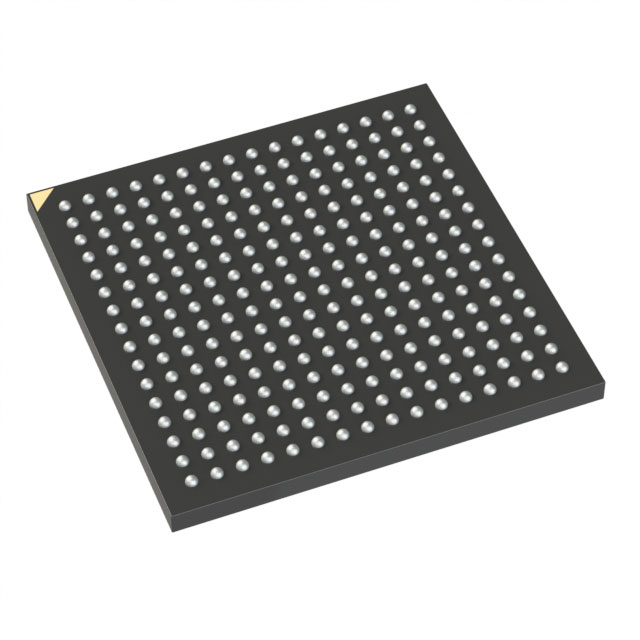

Higher Logic Density for Increased System

Integration

12K to 84K LUTs

197 to 365 user programmable I/O

Embedded SERDES

270 Mb/s, up to 3.2 Gb/s, SERDES interface

(ECP5)

270 Mb/s, up to 5.0 Gb/s, SERDES interface

(ECP5-5G)

Supports eDP in RDR (1.62 Gb/s) and HDR

(2.7 Gb/s)

Up to four channels per device: PCI Express,

Ethernet (1GbE, SGMII, XAUI), and CPRI

sysDSP™

Fully cascadable slice architecture

12 to 160 slices for high performance multiply

and accumulate

Powerful 54-bit ALU operations

Time Division Multiplexing MAC Sharing

Rounding and truncation

Each slice supports

Half 36 x 36, two 18 x 18 or four

9 x 9 multipliers

Advanced 18 x 36 MAC and

18 x 18 Multiply-Multiply-Accumulate

(MMAC) operations

Flexible Memory Resources

Up to 3.744 Mb sysMEM™ Embedded Block

RAM (EBR)

194K to 669K bits distributed RAM

sysCLOCK Analog PLLs and DLLs

Four DLLs and four PLLs in LFE5-45 and

LFE5-85; two DLLs and two PLLs in LFE5-25

and LFE5-12

Pre-Engineered Source Synchronous I/O

DDR registers in I/O cells

Dedicated read/write levelling functionality

Dedicated gearing logic

Source synchronous standards support

ADC/DAC, 7:1 LVDS, XGMII

High Speed ADC/DAC devices

Dedicated DDR2/DDR3 and LPDDR2/LPDDR3

memory support with DQS logic, up to

800 Mb/s data-rate

Programmable sysI/O™ Buffer Supports Wide

Range of Interfaces

On-chip termination

LVTTL and LVCMOS 33/25/18/15/12

SSTL 18/15 I, II

HSUL12

LVDS, Bus-LVDS, LVPECL, RSDS, MLVDS

subLVDS and SLVS, SoftIP MIPI D-PHY

receiver/transmitter interfaces

Flexible Device Configuration

Shared bank for configuration I/O

SPI boot flash interface

Dual-boot images supported

Slave SPI

TransFR™ I/O for simple field updates

Single Event Upset (SEU) Mitigation Support

Soft Error Detect – Embedded hard macro

Soft Error Correction – Without stopping user

operation

Soft Error Injection – Emulate SEU event to

debug system error handling

System Level Support

IEEE 1149.1 and IEEE 1532 compliant

Reveal Logic Analyzer

On-chip oscillator for initialization and general

use

V core power supply for ECP5, 1.2 V core

power supply for ECP5UM5G