• High-efficiency 32-bit CPU (TMS320C28x)

– 90 MHz (11.11-ns cycle time)

– 16 × 16 and 32 × 32 Multiply and Accumulate

(MAC) operations

– 16 × 16 dual MAC

– Harvard bus architecture

– Atomic operations

– Fast interrupt response and processing

– Unified memory programming model

– Code-efficient (in C/C++ and Assembly)

• Floating-Point Unit (FPU)

– Native single-precision floating-point operations

• Programmable Control Law Accelerator (CLA)

– 32-bit floating-point math accelerator

– Executes code independently of the main CPU

• Viterbi, Complex Math, CRC Unit (VCU)

– Extends C28x instruction set to support

complex multiply, Viterbi operations, and Cyclic

Redundency Check (CRC)

• Embedded memory

– Up to 256KB of flash

– Up to 100KB of RAM

– 2KB of One-Time Programmable (OTP) ROM

• 6-channel Direct Memory Access (DMA)

• Low device and system cost

– Single 3.3-V supply

– No power sequencing requirement

– Integrated power-on reset and brownout reset

– Low-power operating modes

– No analog support pin

• Endianness: Little endian

• JTAG boundary scan support

– IEEE Standard 1149.1-1990 Standard Test

Access Port and Boundary Scan Architecture

• Clocking

– Two internal zero-pin oscillators

– On-chip crystal oscillator/external clock input

– Watchdog timer module

– Missing clock detection circuitry

• Peripheral Interrupt Expansion (PIE) block that

supports all peripheral interrupts

• Three 32-bit CPU timers

• Advanced control peripherals

• Up to 8 Enhanced Pulse-Width Modulator (ePWM)

modules

– 16 PWM channels total (8 HRPWM-capable)

– Independent 16-bit timer in each module

• Three input Enhanced Capture (eCAP) modules

• Up to 4 High-Resolution Capture (HRCAP)

modules

• Up to 2 Enhanced Quadrature Encoder Pulse

(eQEP) modules

• 12-bit Analog-to-Digital Converter (ADC), dual

Sample-and-Hold (S/H)

– Up to 3.46 MSPS

– Up to 16 channels

• On-chip temperature sensor

• 128-bit security key and lock

– Protects secure memory blocks

– Prevents reverse-engineering of firmware

• Serial port peripherals

– Two Serial Communications Interface (SCI)

[UART] modules

– Two Serial Peripheral Interface (SPI) modules

– One Inter-Integrated-Circuit (I2C) bus

– One Multichannel Buffered Serial Port (McBSP)

bus

– One Enhanced Controller Area Network

(eCAN)

– Universal Serial Bus (USB) 2.0

(see Device Comparison for availability)

• Full-speed device mode

• Full-speed or low-speed host mode

• Up to 54 individually programmable, multiplexed

General-Purpose Input/Output (GPIO) pins with

input filtering

• Advanced debug features

– Analysis and breakpoint functions

– Real-time debug through hardware

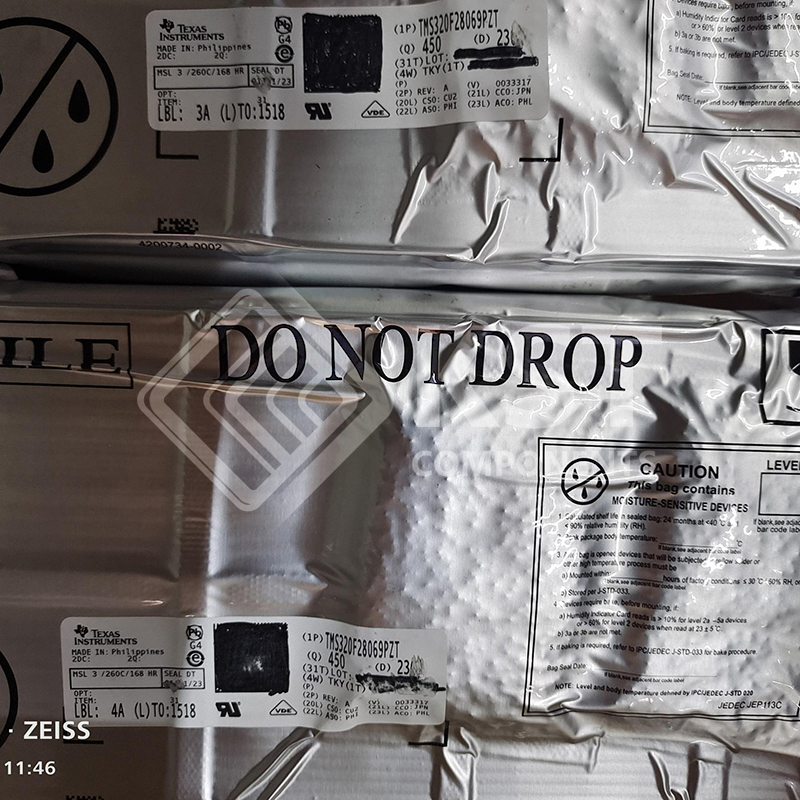

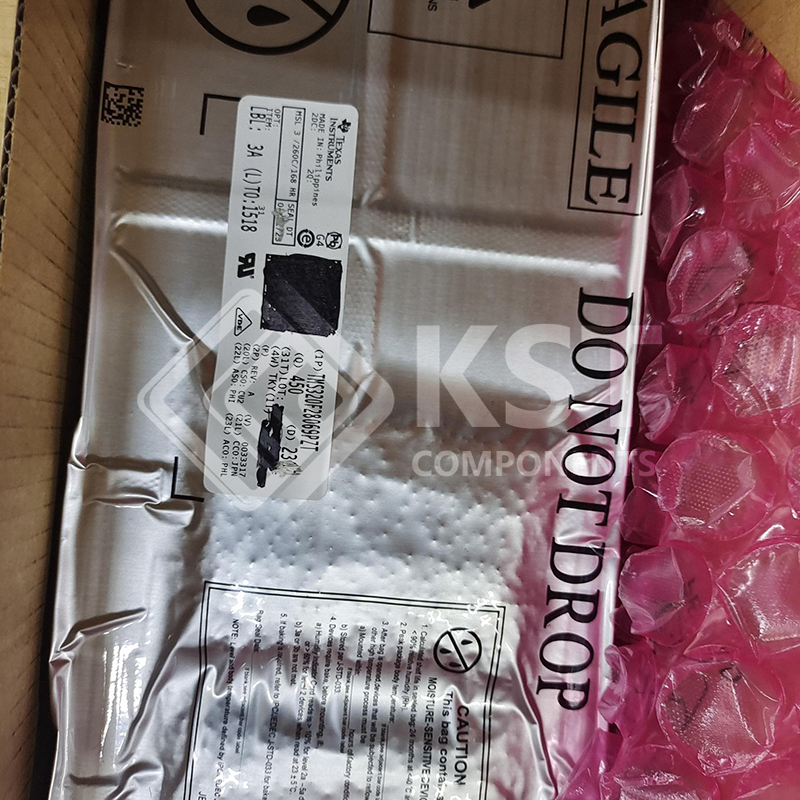

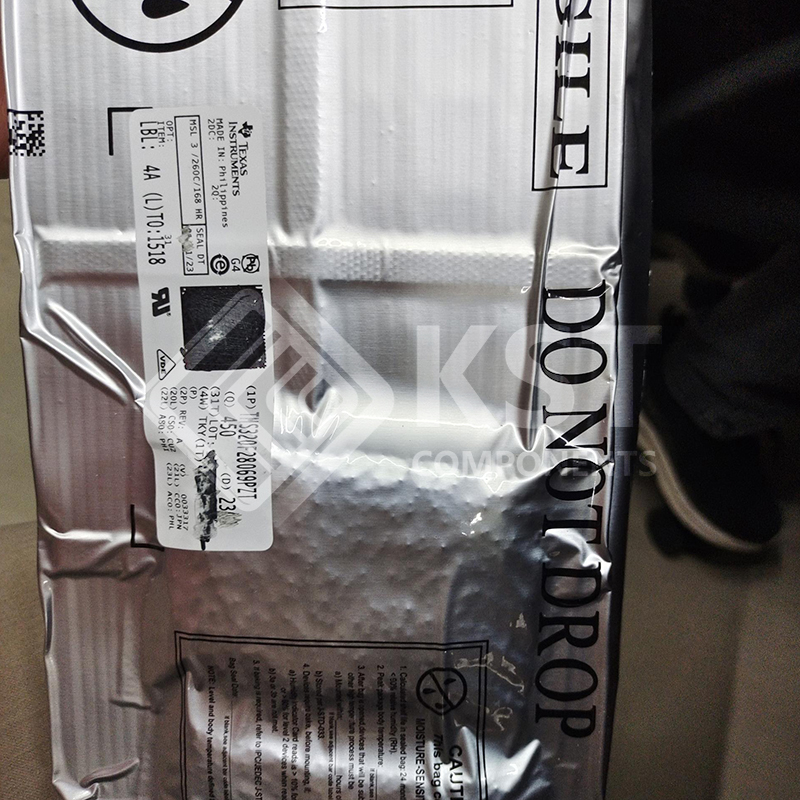

• Package options

– 80-pin PFP and 100-pin PZP PowerPAD™

Thermally Enhanced Thin Quad Flatpacks

(HTQFPs)

– 80-pin PN and 100-pin PZ Low-Profile Quad

Flatpacks (LQFPs)

• Temperature options

– T: –40°C to 105°C

– S: –40°C to 125°C

– Q: –40°C to 125°C (AEC Q100 qualification for

automotive applications)