• Single 2.3 V – 3.6 V supply

• Serial Peripheral Interface (SPI) compatible

• Supports SPI modes 0 and 3

• Supports RapidS™ operation

• Continuous read capability through entire array

• Up to 85 MHz

• Low-power read option up to 15 MHz

• Clock-to-output time (tV) of 6ns maximum

• User configurable page size

• 512 bytes per page

• 528 bytes per page (default)

• Page size can be factory pre-configured for 512 bytes

• Two fully independent SRAM data buffers (512/528 bytes)

• Flexible programming options

• Byte/Page Program (1 to 512/528 bytes) directly into main memory

• Buffer Write

• Buffer to Main Memory Page Program

• Flexible erase options

• Page Erase (512/528 bytes)

• Block Erase (4 kB)

• Sector Erase (64 kB)

• Chip Erase (32 Mbits)

• Program and Erase Suspend/Resume

• Advanced hardware and software data protection features

• Individual sector protection

• Individual sector lock-down to make any sector permanently read-only

• 128-byte, One-Time Programmable (OTP) Security Register

• 64 bytes factory programmed with a unique identifier

• 64 bytes user programmable

• Hardware and software controlled reset options

• JEDEC Standard Manufacturer and Device ID Read

• Low-power dissipation

• 400 nA Ultra-Deep Power-Down current (typical)

• 3 μA Deep Power-Down current (typical)

• 25 μA Standby current (typical)

• 7 mA Active Read current (typical)

• Endurance: 100,000 program/erase cycles per page minimum

• Data retention: 20 years

• Green (Pb/Halide-free/RoHS compliant) packaging options

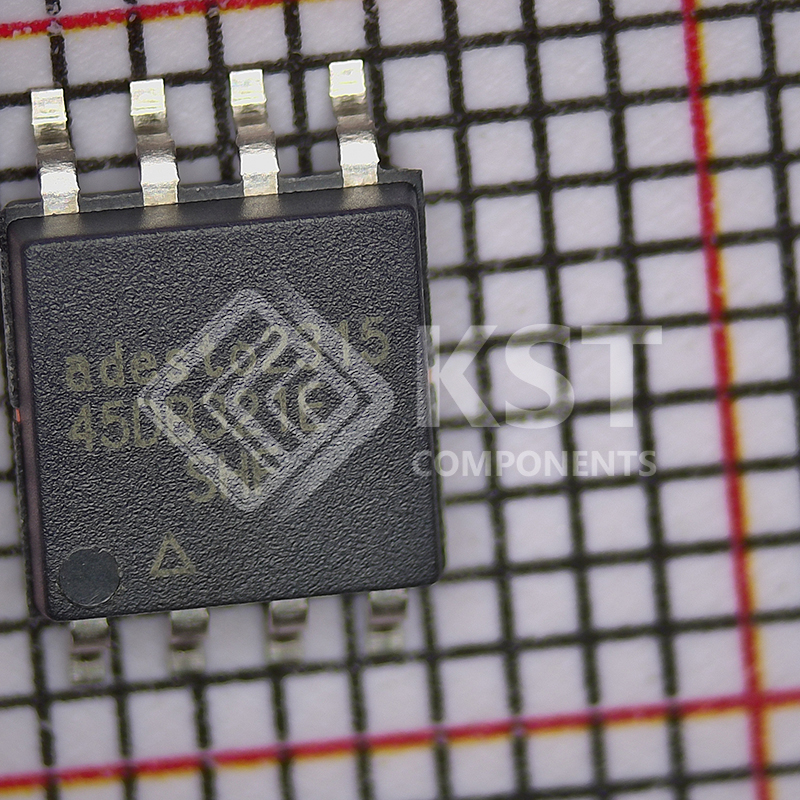

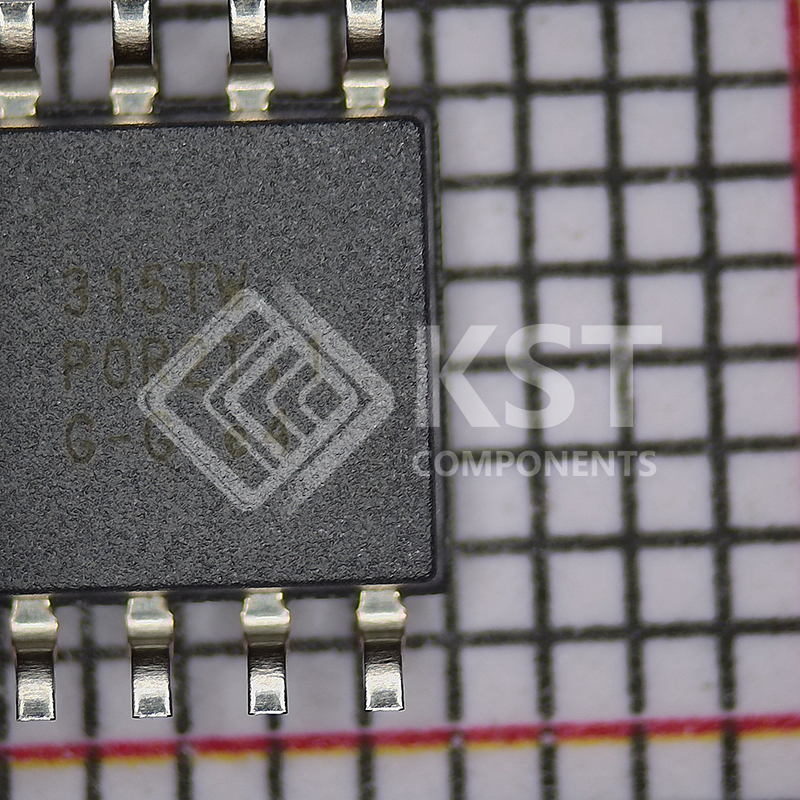

• 8-lead SOIC (208-mil wide)

• 8-pad Ultra-thin DFN (5 x 6 x 0.6 mm)

• 8-pad DFN (6 x 8 x 1.0 mm)

• Die in Wafer Form