• 24-Bit, Low-Power Sigma-Delta ADC

• True Continuous Background Calibration at all

Gains

• In-Place System Calibration Using Expected

Value Programming

• Low-Noise Programmable Gain (1x to 128x)

• Continuous Background Open / Short and Out-ofRange Sensor Diagnostics

• 8 Output Data Rates (ODR) With Single-Cycle

Settling

• 2 Matched Excitation Current Sources From 100

µA to 1000 µA (LMP90100/LMP90098)

• 4-DIFF / 7-SE Inputs (LMP90100/LMP90099)

• 2-DIFF / 4-SE Inputs (LMP90098/LMP90097)

• 7 General-Purpose Input/Output Pins

• Chopper-Stabilized Buffer for Low Offset

• SPI 4/3-wire With CRC Data Link Error Detection

• 50-Hz to 60-Hz Line Rejection at ODR

≤13.42 SPS

• Independent Gain and ODR Selection per

Channel

• Supported by WEBENCH® Sensor AFE Designer

• Automatic Channel Sequencer

• Key Specifications

– ENOB/NFR Up to 21.5/19 Bits

– Offset Error (Typical) 8.4 nV

– Gain Error (Typical) 7 ppm

– Total Noise < 10 µV-rms

– Integral Nonlinearity (INL Maximum) ± 15 ppm

of FSR

– Output Data Rates (ODR) 1.6775 – 214.65

SPS

– Analog Voltage, VA 2.85 to 5.5 V

– Operating Temp Range –40°C to 125°C

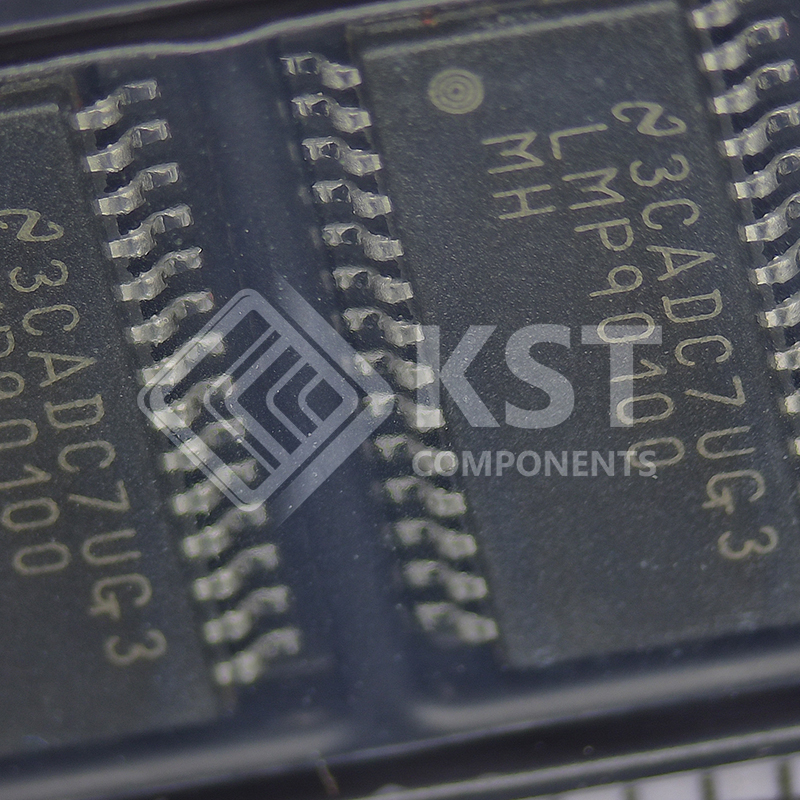

– 28-Pin HTSSOP Exposed Pad