• Provides bidirectional voltage translation with no direction pin

• Less than 1.5 ns maximum propagation delay

• Allows voltage level translation between:

– 1.0 V Vref(A) and 1.8 V, 2.5 V, 3.3 V or 5 V Vref(B)

– 1.2 V Vref(A) and 1.8 V, 2.5 V, 3.3 V or 5 V Vref(B)

– 1.8 V Vref(A) and 3.3 V or 5 V Vref(B)

– 2.5 V Vref(A) and 5 V Vref(B)

– 3.3 V Vref(A) and 5 V Vref(B)

• Low 3.5 Ω ON-state connection between input and output ports provides less signal

distortion

• 5 V tolerant I/O ports to support mixed-mode signal operation

• High-impedance An and Bn pins for EN = LOW

• Lock-up free operation

• Flow through pinout for ease of printed-circuit board trace routing

• ESD protection exceeds 3.5 kV HBM per JESD22-A114 and 1000 V CDM per JESD22-

C101

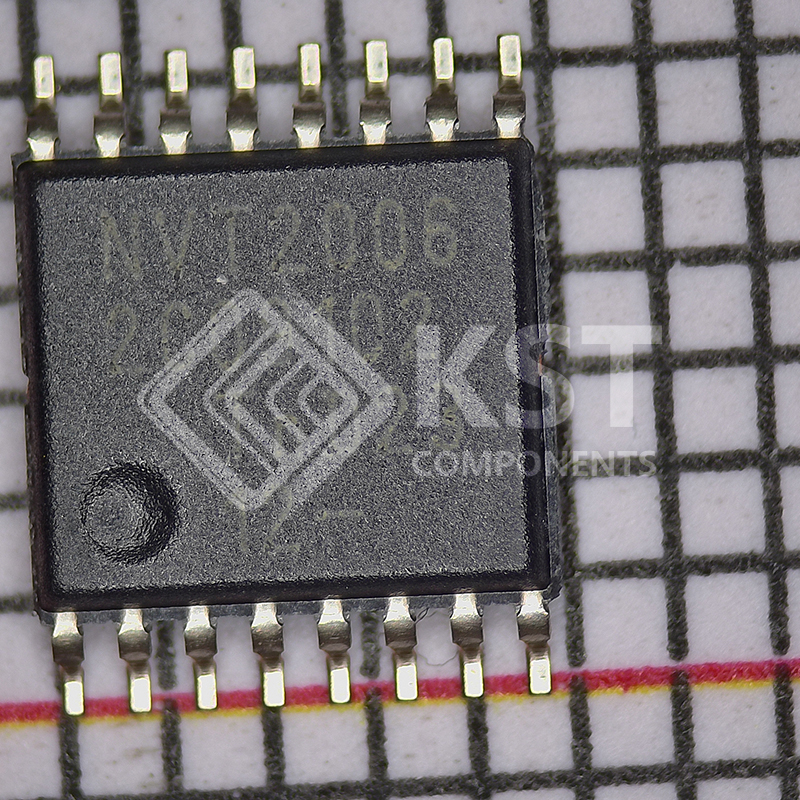

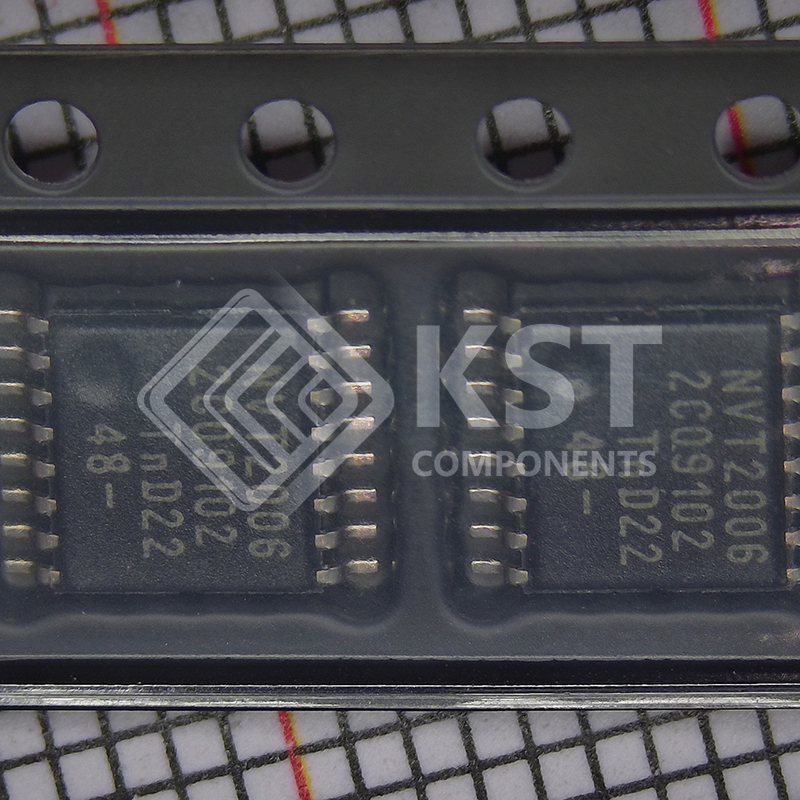

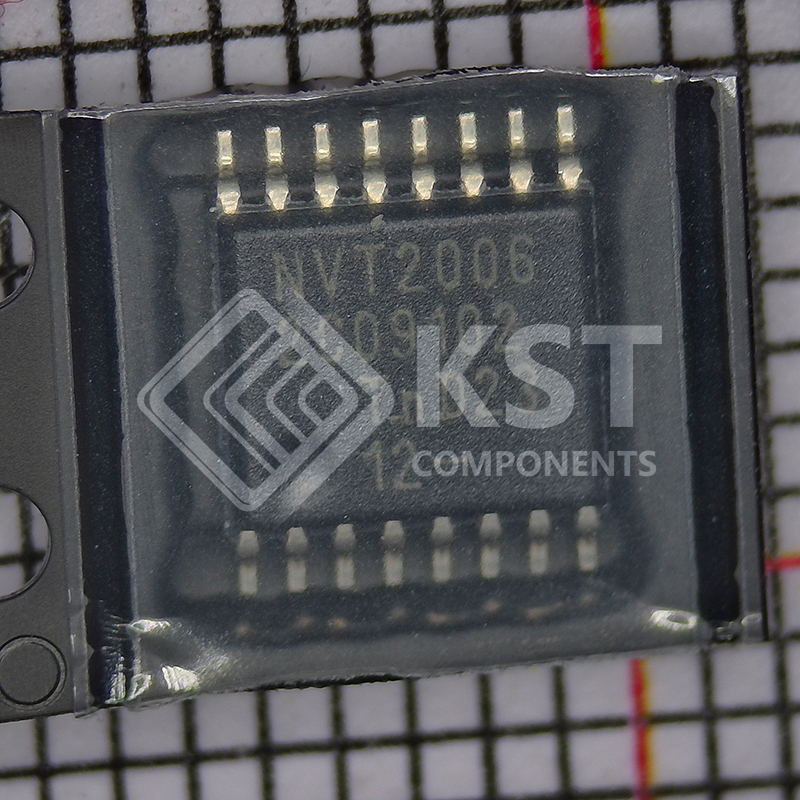

• Packages offered: TSSOP10, DHVQFN16, HVQFN16, TSSOP16