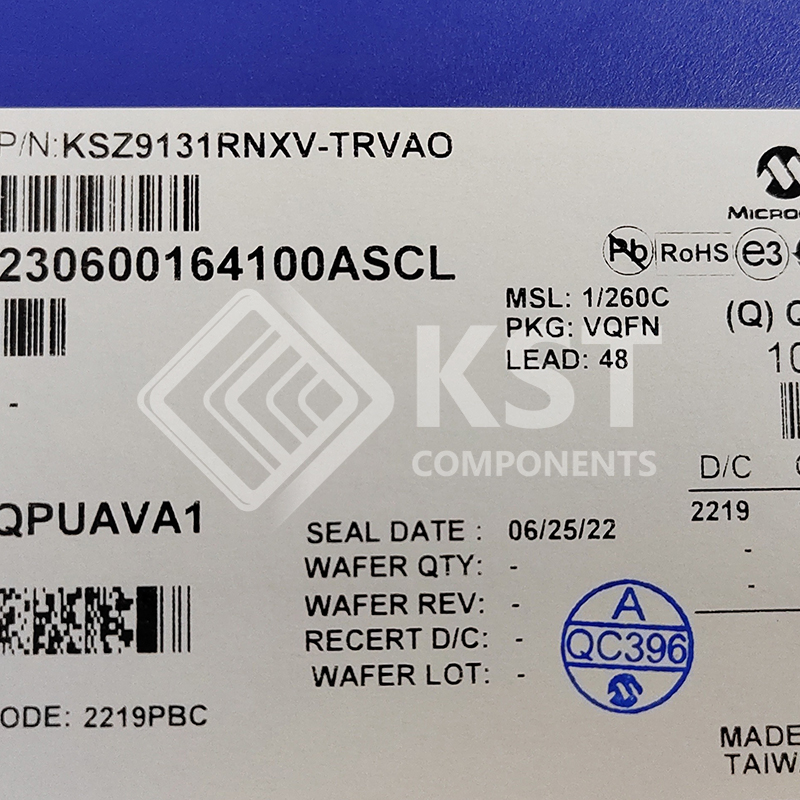

• Single-Chip 10/100/1000 Mbps Ethernet Transceiver Suitable for IEEE 802.3 Applications

• RGMII Timing Supports On-Chip Delay According

to RGMII Version 2.0, with Programming Options

for External Delay and Making Adjustments and

Corrections to TX and RX Timing Paths

• RGMII with 3.3V/2.5V/1.8V Tolerant I/Os

• Auto-Negotiation to Automatically Select the

Highest Link-Up Speed (10/100/1000 Mbps) and

Duplex (Half/Full)

• On-Chip Termination Resistors for the Differential

Pairs

• On-Chip LDO Controller to Support Single 3.3V

Supply Operation – Requires Only One External

FET to Generate 1.2V for the Core

• Jumbo Frame Support Up to 16 KB

• 125 MHz Reference Clock Output

• Energy-Detect Power-Down Mode for Reduced

Power Consumption When Cable is Not Attached

• Energy Efficient Ethernet (EEE) Support with

Low-Power Idle (LPI) Mode and Clock Stoppable

for 100BASE-TX/1000BASE-T and Transmit

Amplitude Reduction with 10BASE-Te Option

• Wake-On-LAN (WOL) Support with Robust

Custom-Packet Detection

• Programmable LED Outputs for Link, Activity, and

Speed

• Baseline Wander Correction

• Quiet-WIRE® EMI Reduction (100BASE-TX)

• LinkMD® TDR-based Cable Diagnostic to Identify

Faulty Copper Cabling

• Signal Quality Indication

• Parametric NAND Tree Support to Detect Faults

Between Chip I/Os and Board

• Loopback Modes for Diagnostics

• Automatic MDI/MDI-X Crossover to Detect and

Correct Pair Swap at All Speeds of Operation

• Automatic Detection and Correction of Pair

Swaps, Pair Skew, and Pair Polarity

• MDC/MDIO Management Interface for PHY Register Configuration

• Interrupt Pin Option

• Power-Down and Power-Saving Modes

• Operating Voltages

– Core (DVDDL, AVDDL, AVDDL_PLL): 1.2V

(External FET or Regulator)

– VDD I/O (DVDDH): 3.3V, 2.5V, or 1.8V

– Transceiver (AVDDH): 3.3V or 2.5V

• AEC-Q100 Grade 3 (KSZ9131RNXU) and Grade

2 (KSZ9131RNXV) Qualified for Automotive

Applications

• 48-pin VQFN (7 mm × 7 mm) Package