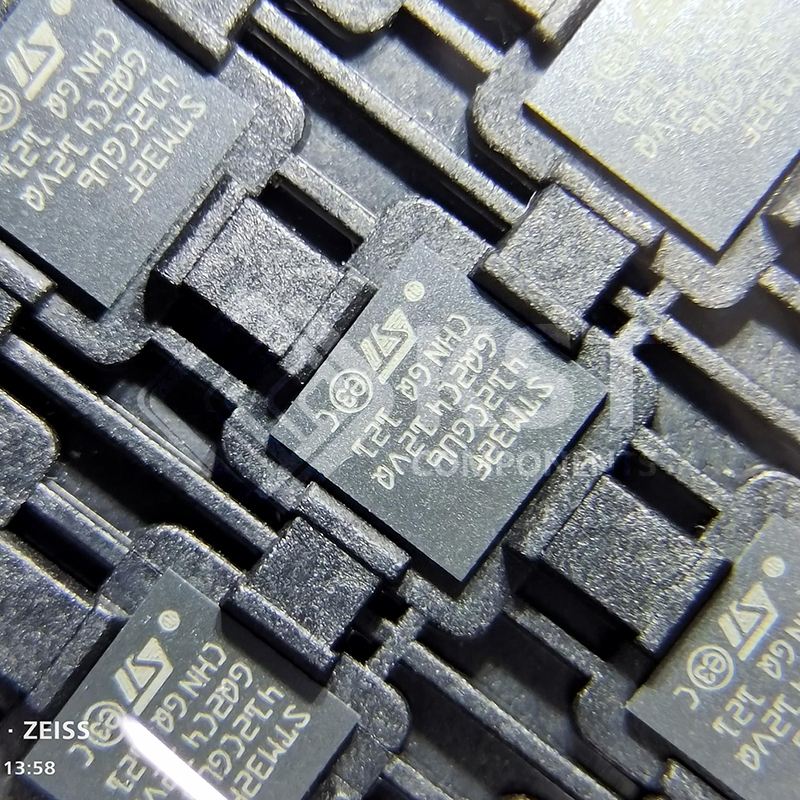

• Includes ST state-of-the-art patented

technology

• Dynamic efficiency line with BAM (Batch

acquisition mode)

• Core: Arm® 32-bit Cortex®-M4 CPU with FPU,

Adaptive real-time accelerator (ART

Accelerator™) allowing 0-wait state execution

from flash memory, frequency up to 100 MHz,

memory protection unit,

125 DMIPS/1.25 DMIPS/MHz (Dhrystone 2.1),

and DSP instructions

• Memories

– Up to 1 Mbyte of flash memory

– 256 Kbytes of SRAM

– Flexible external static memory controller

with up to 16-bit data bus: SRAM, PSRAM,

NOR flash memory

– Dual mode Quad-SPI interface

• LCD parallel interface, 8080/6800 modes

• Clock, reset and supply management

– 1.7 V to 3.6 V application supply and I/Os

– POR, PDR, PVD and BOR

– 4-to-26 MHz crystal oscillator

– Internal 16 MHz factory-trimmed RC

– 32 kHz oscillator for RTC with calibration

– Internal 32 kHz RC with calibration

• Power consumption

– Run: 112 µA/MHz (peripheral off)

– Stop (Flash in Stop mode, fast wakeup

time): 50 µA typical at 25 °C; 75 µA max at

25 °C

– Stop (flash memory in Deep power down

mode, slow wakeup time): down to 18 µA

at 25 °C; 40 µA max at 25 °C

– Standby: 2.4 µA at 25 °C / 1.7 V without

RTC; 12 µA at 85 °C at 1.7 V

– VBAT supply for RTC: 1 µA at 25 °C

1×12-bit, 2.4 MSPS ADC: up to 16

channels

• 2x digital filters for sigma delta modulator,

4x PDM interfaces, stereo microphone support

• General-purpose DMA: 16-stream DMA

• Up to 17 timers: up to twelve 16-bit timers, two

32-bit timers up to 100 MHz each with up to

four IC/OC/PWM or pulse counter and

quadrature (incremental) encoder input, two

watchdog timers (independent and window),

one SysTick timer

• Debug mode

– Serial wire debug (SWD) and JTAG

– Cortex®-M4 Embedded Trace Macrocell™

• Up to 114 I/O ports with interrupt capability

– Up to 109 fast I/Os up to 100 MHz

– Up to 114 five V-tolerant I/Os

• Up to 17 communication interfaces

– Up to 4x I2C interfaces (SMBus/PMBus)

– Up to 4 USARTs (2 x 12.5 Mbit/s,

2 x 6.25 Mbit/s), ISO 7816 interface, LIN,

IrDA, modem control)

– Up to 5 SPI/I2Ss (up to 50 Mbit/s, SPI or

I2S audio protocol), out of which 2 muxed

full-duplex I2S interfaces

– SDIO interface (SD/MMC/eMMC)

– Advanced connectivity: USB 2.0 full-speed

device/host/OTG controller with PHY

– 2x CAN (2.0B Active)

• True random number generator

• CRC calculation unit

• 96-bit unique ID

• RTC: subsecond accuracy, hardware calendar

• All packages are ECOPACK2 compliant