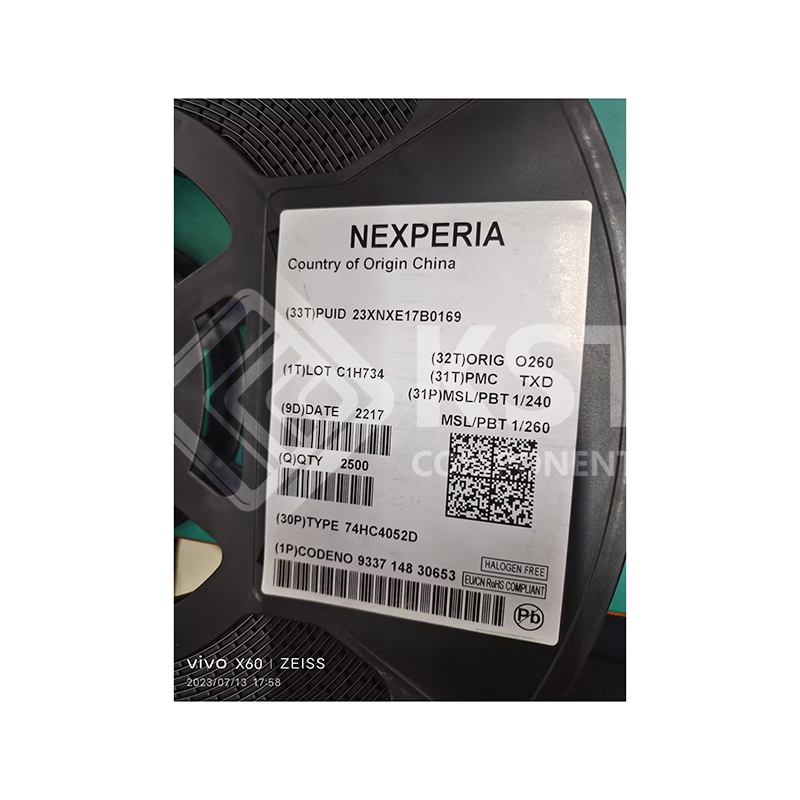

• Wide analog input voltage range from -5 V to +5 V

• CMOS low power dissipation

• High noise immunity

• Latch-up performance exceeds 100 mA per JESD 78 Class II Level B

• Low ON resistance:

• 80 Ω (typical) at VCC – VEE = 4.5 V

• 70 Ω (typical) at VCC – VEE = 6.0 V

• 60 Ω (typical) at VCC – VEE = 9.0 V

• Logic level translation: to enable 5 V logic to communicate with ±5 V analog signals

• Typical ‘break before make’ built-in

• Complies with JEDEC standards:

• JESD8C (2.7 V to 3.6 V)

• JESD7A (2.0 V to 6.0 V)

• Input levels:

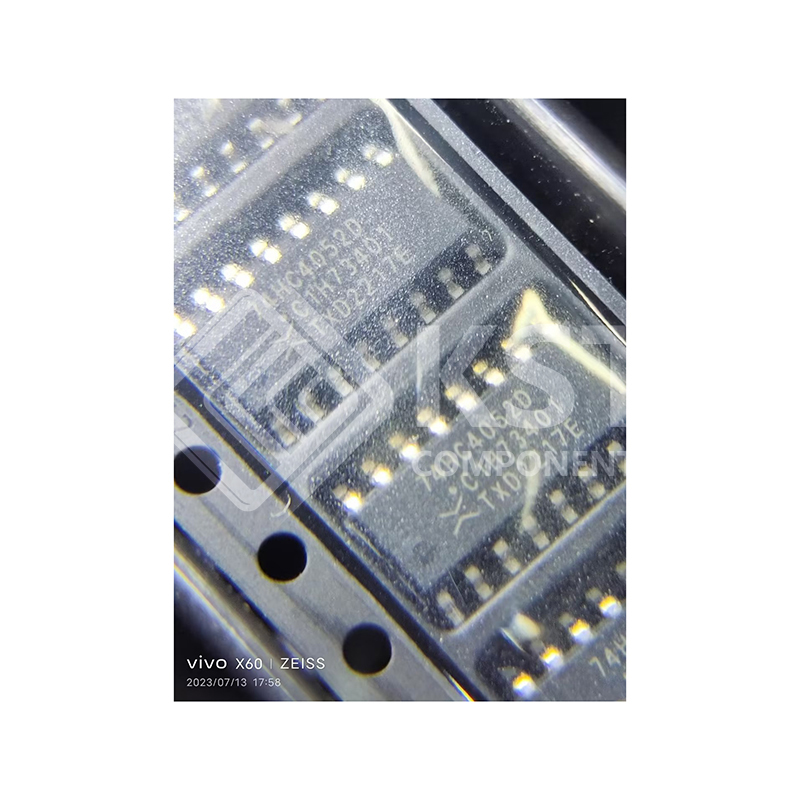

• For 74HC4052: CMOS level

• For 74HCT4052: TTL level

• ESD protection:

• HBM: ANSI/ESDA/JEDEC JS-001 class 2 exceeds 2000 V

• CDM: ANSI/ESDA/JEDEC JS-002 class C3 exceeds 1000 V

• Specified from -40 °C to +85 °C and -40 °C to +125 °C